Il sito ExtremeTech fa un riepilogo di alcune nuove tecnologie per le memorie del futuro, che hanno a che fare con le RAM e delle quali molto probabilmente sentiremo parlare molto da quest’anno in poi. Rispetto alle ormai consolidate memorie DDR3/LPDDR3, gli standard DDR4 e LPDDR4 consentono di migliorare e fare evolvere l’esistente design delle DRAM permettendo nuove prestazioni, miglioramenti in termini di risparmio energetico e aumento della velocità di trasmissione dei dati.

Le memorie DDR4 non tagliano ad ogni modo ancora i ponti con il passato essendo per certi versi limitate per loro natura da soluzioni ideate quando le CPU erano ancora single-core; le prime memorie DIMM tipo SDRAM supportavano velocità di 66 MHz e larghezza di banda di 533 MB al secondo; da allora fino alle nuove DDR4-3200 la tecnologia ha compiuto doversi balzi in avanti, ora arrivando a supportare velocità di clock di 1.600 MHz e larghezza di banda fino a 25,6 GB/s. Si tratta di un incremento di 48x in circa 20 anni e mentre si dibatte se c’è spazio per migliorare ancora (qualcuno già accenna alle DDR5) nuove tecnologie promettono di sfruttare larghezza di banda ancora maggiore, riducendo allo stesso tempo anche i consumi.

Uno standard appoggiato dallo JEDEC (organismo per la standardizzazione dei semiconduttori) e da Samsung è il Wide I/O, presentato nel 2011 con target specificatamente i SoC dei dispositivi mobili, in grado di sfruttare la massima larghezza di banda possibile e ridurre al minimo i consumi. Questa tecnologia interessa in particolare i produttori di smartphone e tablet: i display con risoluzioni sempre più elevata, ad esempio, richiedono maggiore potenza e consumi ridotti. La prima versione di questo standard per le memorie è stata presentata come detto nel 2011 ma si è già passati al Wide I/O 2 e al Wide I/O 3, tutte e due in grado di superare le capacità di trasferimento dati di altri sistemi disponibili ora.

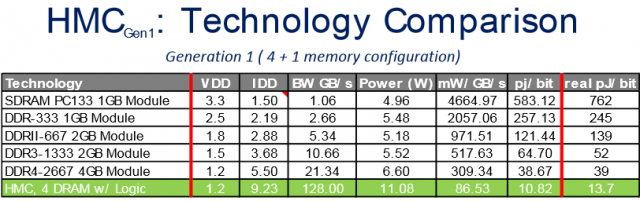

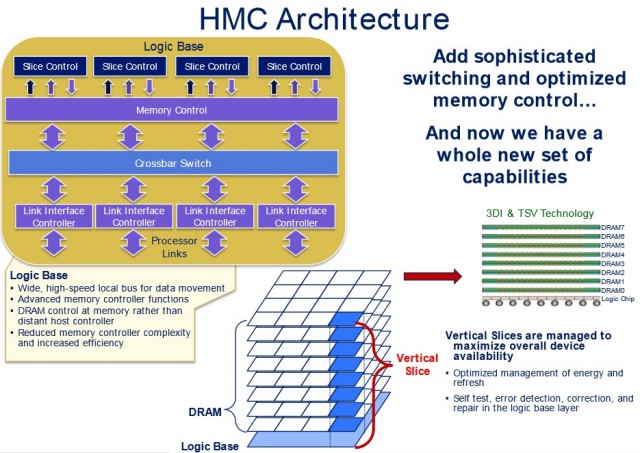

Intel e Micron propongono invece l’Hybrid Memory Cube (HMC), conduttori verticali che collegano elettricamente una pila di singoli chip per combinare dispositivi logici ad alte prestazioni con la DRAM. Con questo standard è possibile spostare i dati fino a 15 volte più velocemente rispetto a un modulo DDR3 e utilizzare fino al 70% di energia in meno e il 90% in meno di spazio rispetto alle attuali tecnologie di memoria. Secondo i promotori di questo standard, le funzionalità associate all’interfaccia astratta, l’affidabilità avanzata, la disponibilità e serviceability (RAS) dell’HMC riducono la complessità e semplificano il design dei dispositivi. L’HMC non è supportata dallo JEDEC ma tra le centinaia di partner che hanno mostrato interesse, ci sono: Micron, Microsoft, Altera, ARM, Intel, HP, Xilinx e anche Samsung. Nelle specifica 2.0 si parla di larghezza di banda di 160 GB/s usando il 70% di energia per bit in meno rispetto alle tecnologie esistenti.

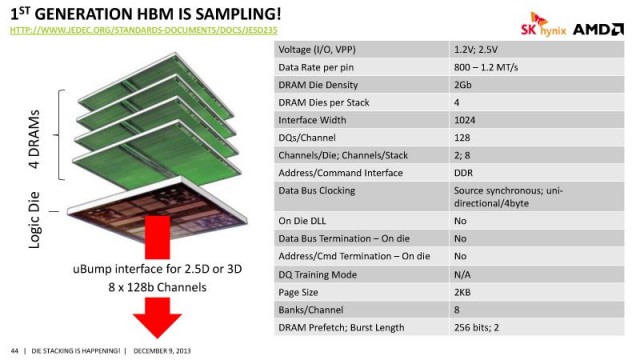

Proposta ancora diversa è l’High Bandwidth Memory, appoggiata da Hynix, AMD e Nvidia. Particolarmente adatta per l’uso nelle GPU, questa tecnologia sarà sfruttata da Nvidia per Pascal, architettura attesa per il 2016; anche AMD pare stia lavorando con la tecnologia in questione ma non è stato ad ogni modo fatto nessun annuncio specifico. L’High Bandwidth Memory promette il supporto a larghezza di banda tra i 512 GB/s e 1 TB/s, un grande passo in avanti rispetto alla banda passante di 336 GB/s delle GPU Titan Black.