Nell’ambito del 30° North America Technology Symposium 2024 dell’azienda, TSMC ha annunciato un nuovo processo per semiconduttori, packaging all’avanguardia e innovazioni per il 3D IC che permettono di migliorare l’efficienza nei processi di design, e di sfruttare tecnologie di 3D silicon stacking e packaging ancora più avanzate.

Tra gli annunci, un processo produttivo denominato “A16”, un nodo a 1,6nm che combina l’architettura Super Power Rail con i transistor nanosheet (evoluzione del gate-all-around che permette di impilare verticalmente le estremità del transistor anziché solamente di lato) che dovremmo vedere in nuovi prodotti a partire dal 2026.

TSMC riferisce che la tecnologia A16 permette di migliorare densità e performance, e che rispetto al nodo N2P (2nm) prevede migliorie nell’ordine dell’8%-10% a parità di Vdd (positive power supply voltage), una riduzione della potenza richiesta del 15-20% a parità di velocità e migliorie fino a 1,10x in termini di densità per i prodotti destinati ai data center.

Apple ha sempre sfruttato per prima i nodi produttivi di TSMC; è stata, ad esempio, la prima a usare il nodo a 3nm per l’A17 Pro dell’iPhone 15 Pro e iPhone 15 Pro Max, ed è probabile che sarà così anche per i nuovi nodi, per ottenere chip che saranno sfruttati in futuri dispositivi.

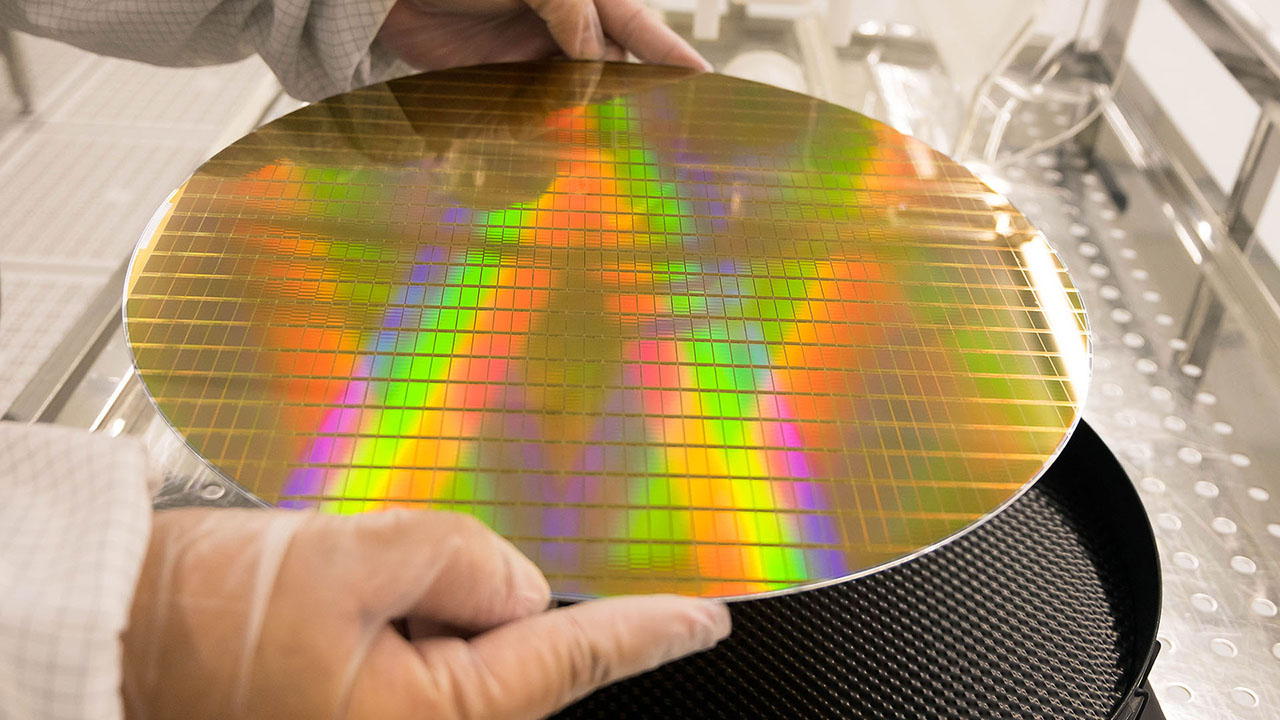

TSMC ha annunciato anche il rollout della tecnologia System-on-Wafer (SoW), una soluzione innovativa che promette “prestazioni rivoluzionarie” a livello di wafer e di rispondere ai futuri requisiti dell’intelligenza artificiale per i data center hyperscaler. La tecnologia SoW è già in produzione, è a sua volta basata sulla Fan-Out (InFO), con i componenti del chip montati direttamente nei wafer di silicio (riducendo le dimensioni fisiche e ottimizzando l’efficienza elettrica/termica). Ulteriori progressi su quest’ultimo versante sono previsti con una tecnologia denominata CoWoS prevista per il 2027.

Per tutti gli articoli dedicati a TSMC, fate riferimento a questo collegamento.