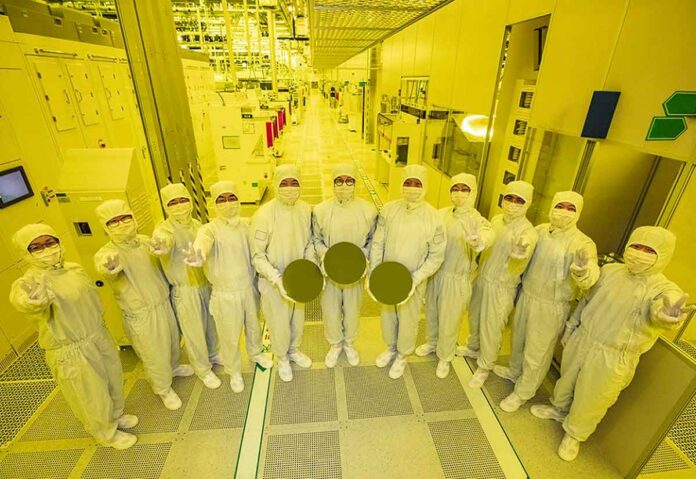

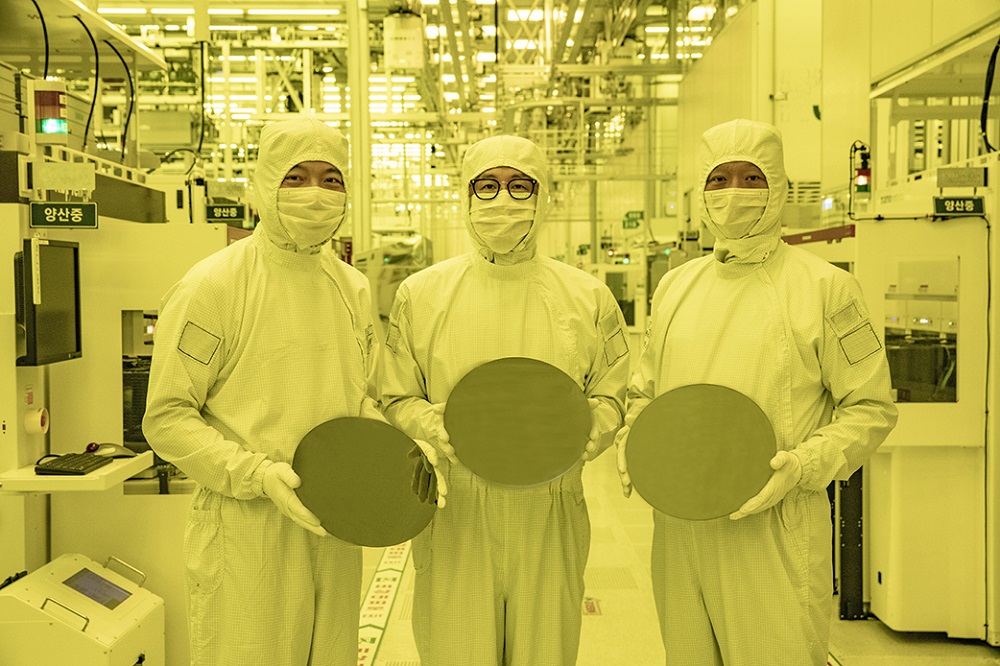

Da anni TSMC è all’avanguardia nelle tecnologie di costruzione dei processori, ma questa volta Samsung è riuscita ad anticipare il concorrente annunciando di avere avviato la produzione in serie di chip con processo produttivo a 3 nanometri (nm), il nodo più avanzato disponibile per la produzione a contratto (chip creati per conto di terze parti).

L’azienda sudcoreana riferisce che, rispetto al processo a 5nm, il nodo a 3nm permette di ridurre il consumo energetico del 45%, offrire migliorie in termini di prestazioni del 23% e allo stesso tempo ridurre l’area superficiale del 16%.

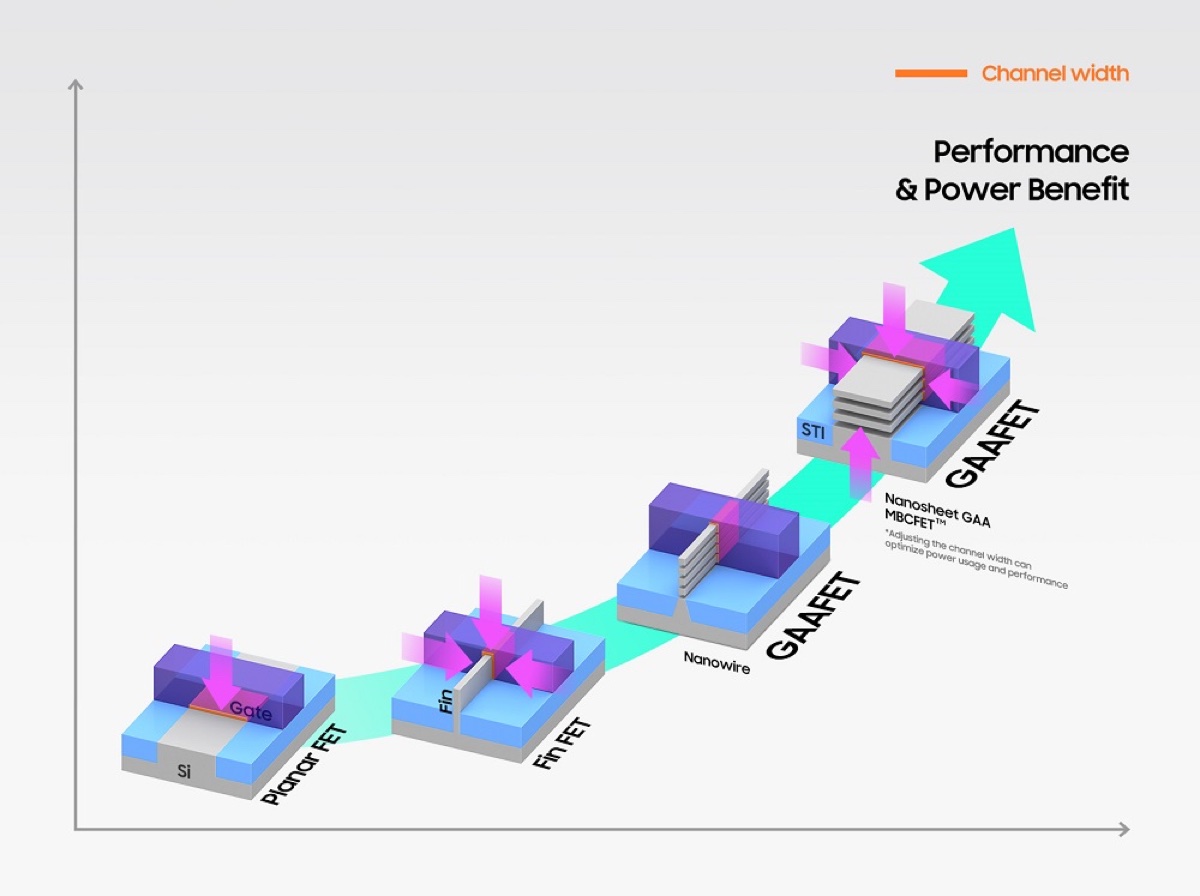

Il nodo produttivo di Samsung sfrutta una sua architettura dei transitor gate-all-around (GAA) denominata Multi-Bridge-Channel FET (MBCFET), che prevede migliorie rispetto all’architettura FinFET, a partire dai canali, completamente circondati da gate, e la rimozione di alcuni materiali, elemento che consente una regolazione più precisa della loro larghezza.

L’azienda sudcoreana riferisce che il design è flessibile e i canali possono essere regolati per soddisfare al meglio le esigenze dei clienti. È già prevista una seconda generazione, promettendo ulteriori miglioramenti in termini di consumi, performance e area superficiale utilizzata. Non è chiaro quali siano i primi clienti di Samsung ma l’azienda ha riferito che il nodo a 3 nanometri in questione ha come target applicazioni ad alte prestazioni, il low-power computing e che prevede di espandere specificatamente il nodo per l’ambito processori mobili.

Samsung è, insieme a TSMC, una delle più grandi aziende al mondo in grado di produrre chip. Anche la taiwanese TSMC sta da tempo lavorando sul nodo a 3nm, con l’obiettivo di fornire partner come Apple e Qualcomm, sempre alla ricerca di nuovi modi per migliorare prestazioni, ridurre i consumi e la densità dei transistor.

Tra i potenziali clienti di questi nodi ci sono anche AMD e Nvidia che a questo punto non dovrebbero avere problemi di approvvigionamento per i rispettivi chip di punta. Intel, invece, non è riuscita a produrre su larga scala CPU di questo tipo anche se ha registrato un brevetto nel quale si fa riferimento a “stacked forksheet”, una tecnica per impilare l’uno sull’altro i transistor meglio di quanto avviene con l’attuale FinFET e che potrebbe portare l’azienda a scendere nell’arena dei 3nm.

Si prevede che anche Apple impiegherà presto il processo a 3 nanometri di TSMC per realizzare le prossime versioni più potenti del processore Apple Silicon M2 e anche per i primissimi modelli di M3 che sembra seguiranno con tempistiche più brevi rispetto a quanto accaduto per il passaggio da M1 a M2 (qui il confronto tra i due).