IBM ha annunciato che investirà 3 miliardi di dollari nei prossimi 5 anni in due vasti programmi di ricerca e sviluppo, che si propongono di identificare la tecnologia dei chip necessaria per soddisfare i requisiti posti dal cloud computing e le applicazioni Big data.

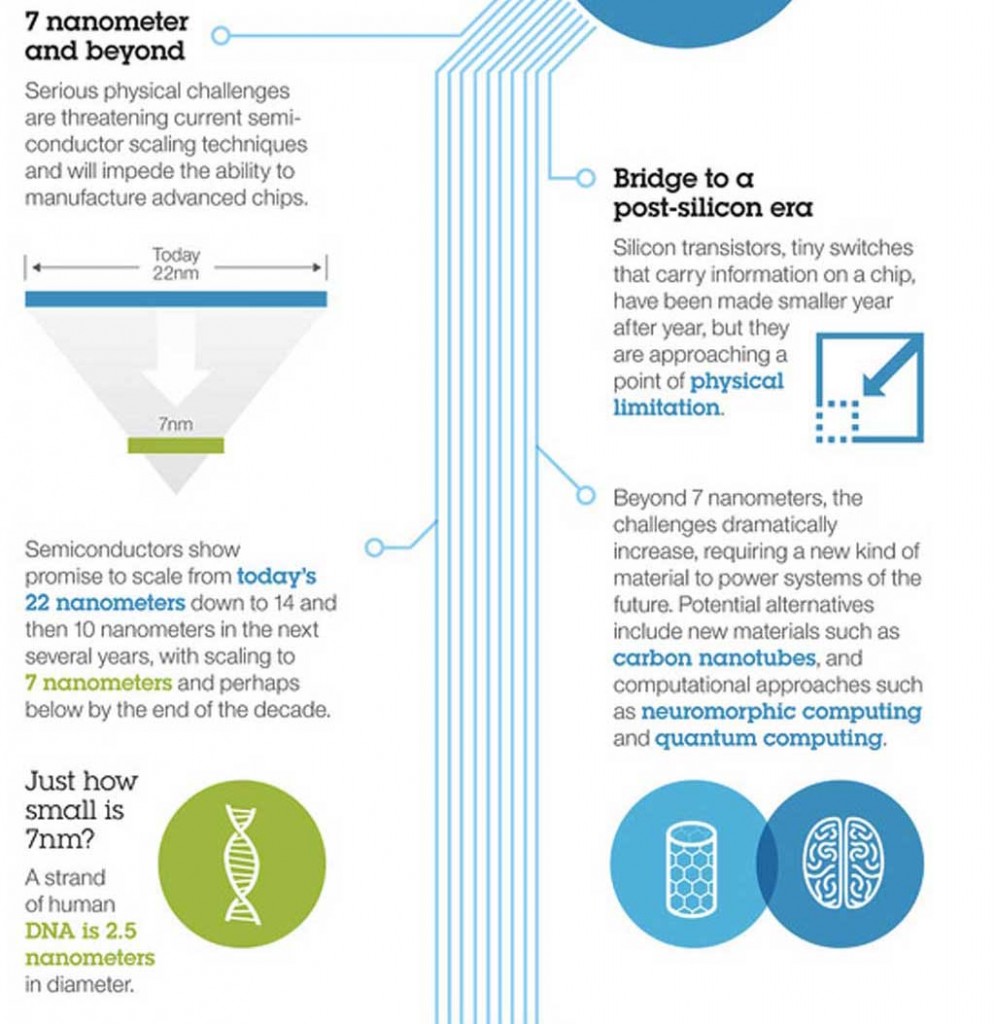

Il primo programma di ricerca riguarda la cosiddetta tecnologia del silicio a “7 nanometri e oltre” e affronterà i problemi dei materiali che attualmente limitano le tecniche utilizzate per ridurre le dimensioni fisiche dei semiconduttori e ostacolano la possibilità di realizzare i chip. La seconda si focalizza sullo sviluppo di tecnologie alternative per i chip dell’era post-silicio, con l’utilizzo di approcci totalmente diversi che, nell’opinione degli ricercatori IBM e di altri esperti, si rendono necessari per via delle limitazioni legate all’impiego del silicio per la fabbricazione dei semiconduttori.

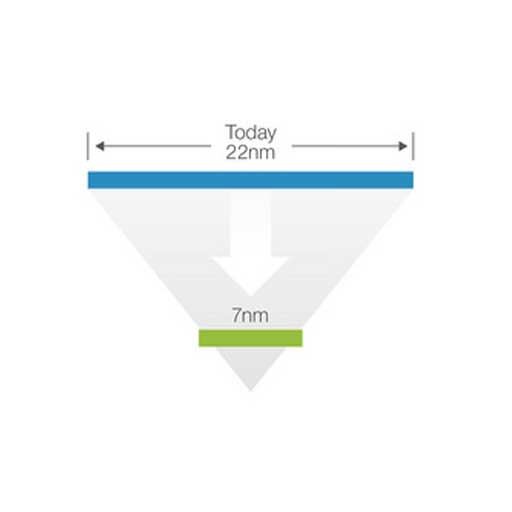

La larghezza di banda, la memoria, la comunicazione ad alta velocità e il consumo di energia dei dispositivi diventano limiti sempre più critici. I ricercatori di IBM e altri esperti di semiconduttori prevedono che, anche se la sfida si prospetta impegnativa, i semiconduttori fanno sperare in una possibile riduzione dei dispositivi dagli attuali 22 nanometri a 14 e poi 10 nanometri nei prossimi anni. Tuttavia, la miniaturizzazione a 7 nanometri e forse oltre, entro la fine del decennio, richiederà un investimento significativo e l’innovazione nelle architetture dei semiconduttori, così come l’invenzione di nuovi strumenti e tecniche per la produzione.

I transistor in silicio, minuscoli switch che trasportano le informazioni su un chip, sono stati rimpiccioliti anno dopo anno, ma si stanno avvicinando al limite fisico. Le dimensioni sempre più piccole, che ora raggiungono la nanoscala, impediranno aumento delle prestazioni, data la natura del silicio e le leggi della fisica. Entro qualche altra generazione, le classiche riduzioni dimensionali non produrranno più i sostanziali vantaggi in termini di minore consumo, minore costo e processori a più elevata velocità a cui il settore è ormai abituato.

Poiché oggi praticamente tutte le apparecchiature elettroniche sono costruite sulla tecnologia CMOS (metallo-ossido semiconduttore complementare), esiste un urgente bisogno di nuovi materiali e configurazioni di architettura dei circuiti compatibili con questi nuovi processi , nel momento la tecnologia attuale si avvicina ai limiti fisici di scalabilità del transistor al silicio.

Oltre i 7 nanometri, le sfide aumentano notevolmente, richiedendo un nuovo tipo di materiale per custruire i sistemi del futuro e nuove piattaforme di calcolo per risolvere problemi oggi di difficile o impossibile soluzione. Le potenziali alternative comprendono nuovi materiali, quali nanotubi di carbonio, e approcci computazionali quali neuromorphic computing, grafene, fotonica del silicio, quantum computing.

Oltre ai nuovi materiali, come inanotubi di carbonio, si richiedono anche nuove architetture e concezioni innovative dei dispositivi per potenziare le prestazioni dei sistemi del futuro. La dissipazione di potenza è una sfida fondamentale per i circuiti nanoelettronici. Una potenziale alternativa agli attuali transistor a effetto di campo di silicio, ad alto consumo di energia, sono i cosiddetti dispositivi ad alta pendenza (steep slope), che potrebbero funzionare a una tensione molto più bassa e dissipare così una quantità di potenza significativamente minore. Per ridurre il consumo energetico in elettronica, i ricercatori stanno conducendo ricerche sui transistor a effetto di campo tunnel (Tunnel Field Effect Transistor, TFET). In questo particolare tipo di transistor, l’effetto di meccanica quantistica del tunnelling tra bande (band-to-band tunneling) è utilizzato per guidare il flusso di corrente attraverso il transistor. I TFET potrebbero realizzare una riduzione di potenza di 100 volte rispetto ai transistor CMOS e l’integrazione dei TFET con la tecnologia MOS potrebbe migliorare i circuiti integrati a bassa potenza.

![iGuide per i regali di Natale - macitynet..ti CTA Natale iGuida [per Settimio] - macitynet.it](https://www.macitynet.it/wp-content/uploads/2025/12/regali-di-natale-consigli-di-macitynet.jpg)