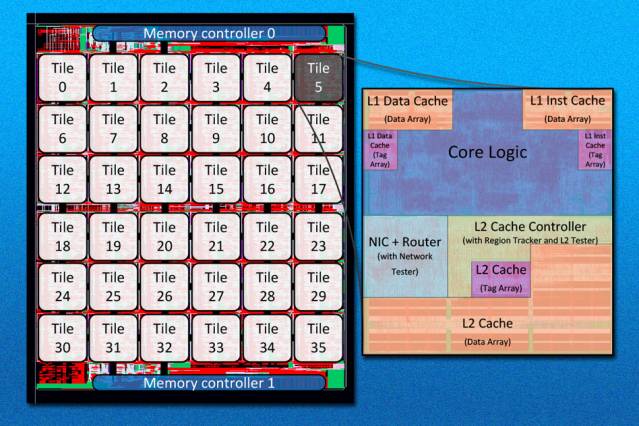

Ricercatori del MIT hanno sviluppato un chip sperimentale con 36 core in cui ognuno di questi ha la peculiarità di comunicare con l’altro sfruttando una sorta di “rete” con il vantaggio di rendere possibili velocità di elaborazione maggiori rispetto a quelle possibili con gli odierni chip multi-core.

Con l’aumentare dei core integrati in un chip, aumenta il problema della comunicazione e del loro coordinamento. Li-Shiuan Peh, Singapore Research Professor of Electrical Engineering and Computer Science al MIT ritiene che i chip multicore del futuro integreranno meccanismi che ricordano un po’ Internet con i vari core gestiti da un router e i dati che viaggiano tra i core sfruttando pacchetti di dimensioni fisse.

All’International Symposium on Computer Architecture di questa settimana, il gruppo guidato da Peh ha mostrato un chip con 36-core, il primo a vantare questa sorta di funzionalità che potremmo definire network-on-chip. Oltre ad implementare in questo alcune delle idee del gruppo, il chip risolve uno dei problemi che in precedenza avevano impedito di disegnare i networks-on-chip: la gestione della coerenza della cache di primo livello, giacché in architetture del genere il problema è la gestione dei dati che “rimbalzerebbero” da una parte all’altra in assenza di un bus che collega i vari core.

Nei chip odierni, tutti i core – tipicamente da due a sei – sono connessi sfruttando un unico collegamento, denominato bus. Quando due core devono comunicare, questi devono ottenere accesso esclusivo al bus. Questo approccio crea problemi all’aumentare dei core: questi, infatti, perdono il loro tempo ad attendere che il bus si liberi, anziché passarlo a eseguire calcoli.

In un network-on-chip, ogni core è connesso solo a quello immediatamente adiacente, garantendo velocità nella propagazione dei dati e offrendo la possibilità di seguire percorsi alternativi in caso di indisponibilità di uno dei core (ognuno si comporta da router per il proprio vicino).

Una sorta di seconda rete coadiuva quella formata dai core, il cui unico fine è di “dichiarare in maniera semplice” quale core ha richiesto dati nella cache, semplificando le operazioni di instradamento da parte della prima rete.

Una delle sfide per gli accademici, sarà convincere l’industria del settore circa la fattibilità delle loro idee. Dopo le fasi di testing dei prototipi, il gruppo di progettisti valuterà le prestazioni nelle applicazioni reali sfruttando una versione di Linux ottimizzata per gestire i 36 core. Todd Austin, professor of electrical engineering and computer science all’University of Michigan dice che “sarebbe sorpreso se per queste tecnologie non si trovasse un utilizzo in prodotti commerciali”.