[banner]…[/banner]

Nel corso dell’IEEE International Electron Device Meeting (IEDM) che si è svolto a San Francisco, ricercatori di Intel hanno descritto l’uso del cobalto per ottimizzare alcuni layer di interconnessione, elemento che permetterebbe di spostare informazioni (bit) in modo più efficiente e dedicare margine ad altri compiti utili, come il processo dei dati.

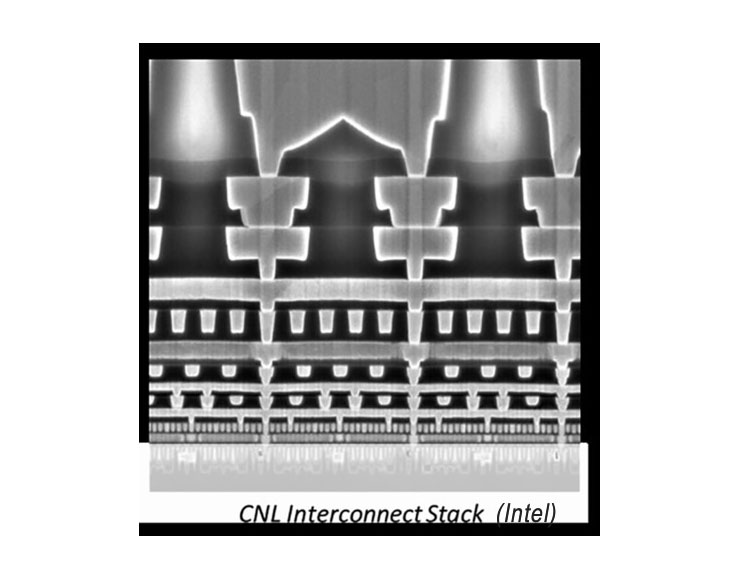

I ricercatori di Intel hanno mostrato una piattaforma tecnologica a 10nm affermando che questa offre “eccellenti performance” a livello di interconnessione e nello scaling da seguire con le norme di progettazione. Hanno dimostrato la piattaforma creando un modulo SRAM d 204Mb con tre diversi tipi di celle di memoria: alta densità 0.0312µm2, basso voltaggio 0.0367µm2 e alte prestazioni da 0.0441µm2. La piattaforma è costruita con processi di litografia FinFET di 3a generazione e di proiezione SAQP (Self-Aligned Quadruple Patterning) per i layer critici che consentono di diminuire la larghezza delle “pinne” (fin) del canale di conduzione che collega emettitore e collettore. Di particolare interesse è l’uso del cobalto per i layer di interconnessione a 10nm, scelta che permetterebbe di ottenere migliorie nell’ordine di 5-10x nel fenomeno dell’elettromigrazione e una riduzione 2x nella resistenza elettrica.

Mancano ancora vari dettagli ma in linea generale l’uso del cobalto come metallo “incapsulatore” potrebbe consentire alla Legge di Moore di rimanere ancora attuale, migliorando affidabilità e prestazioni dei collegamenti di miliardi di transistor che si trovano all’interno di un chip. Ne dovremmo sapere di più nelle prossime settimane.