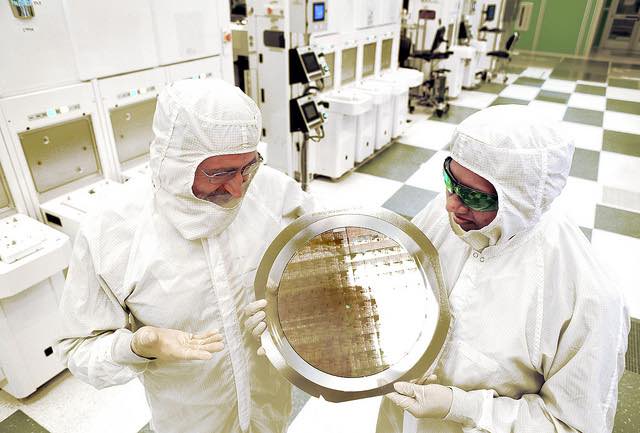

Ricercatori IBM, in collaborazione con i Colleges of Nanoscale Science and Engineering del SUNY Polytechnic Institute, hanno realizzato i primi chip, funzionanti, con processo produttivo a 7 nanometri (nanometri). Questo risultato è stato raggiunto grazie a una partnership pubblico-privato di Big Blue con lo Stato di New York, all’alleanza per lo sviluppo congiunto di Globalfoundries, Samsung e altri fornitori di apparecchiature, ed è frutto dell’investimento quinquennale da 3 miliardi di dollari nella ricerca e nello sviluppo dei chip annunciato da IBM nel 2014. Nell’ambito di questo progetto i ricercatori che lavorano presso il NanoTech Complex del SUNY Poly ad Albany stanno espandendo i limiti della tecnologia dei chip verso la frontiera dei 7 nanometri per far fronte alle nuove sfide introdotte dalle tecnologie del cloud computing, dei Big data e del cognitive computing.

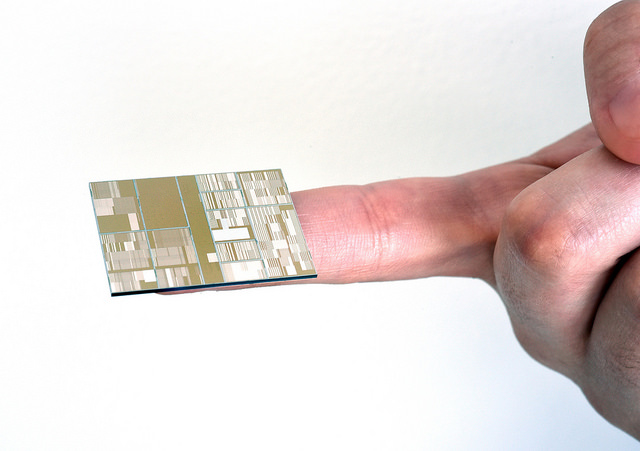

Sviluppare una tecnologia a 7 nm è stata una delle grandi sfide del settore dei semiconduttori. Raggiungere dimensioni così ridotte, attraverso i processi tradizionali, portava finora ad un degrado delle prestazioni del chip che vanificava i benefici attesi dalla riduzione delle dimensioni: prestazioni più elevate, minore fabbisogno di energia e riduzione dei costi (per fattori di scala). I microprocessori che utilizzano la tecnologia a 22 nm e 14 nm sono quelli che troviamo oggi nei server, nei data center cloud e nei dispositivi mobili; la tecnologia a 10 nm è ormai una tecnologia matura, ma i 7 nanometri erano finora rimasti fuori dalla portata per una serie di barriere tecnologiche fondamentali. Molti hanno messo addirittura in dubbio la possibilità di realizzare chip di dimensioni così ridotte ottenendo i vantaggi attesi.

Un chip di prova a 7 nm, con transistor funzionanti, è stato realizzato mediante processi e tecnologia sperimentate per la prima volta dai ricercatori. Lo sviluppo ha richiesto l’introduzione di una serie di innovazioni mai realizzate nel settore, come i transistor con giunzioni miste silicio-germanio (SiGe) e l’integrazione della litografia ultravioletta estrema (EUV) a più livelli. Grazie all’introduzione delle giunzioni SiGe, a nuovi processi per impilarle al di sotto dello spazio di 30 nm e alla piena integrazione della litografia EUV a più livelli, i ricercatori sono riusciti a realizzare miglioramenti vicini al 50 per cento rispetto alla più avanzata tecnologia dei 10 nm di oggi. Questi sforzi potrebbero tradursi in un analogo miglioramento del rapporto potenza/prestazioni per la prossima generazione di chip che verranno impiegati, tra le altre cose, anche nel settore mobile.