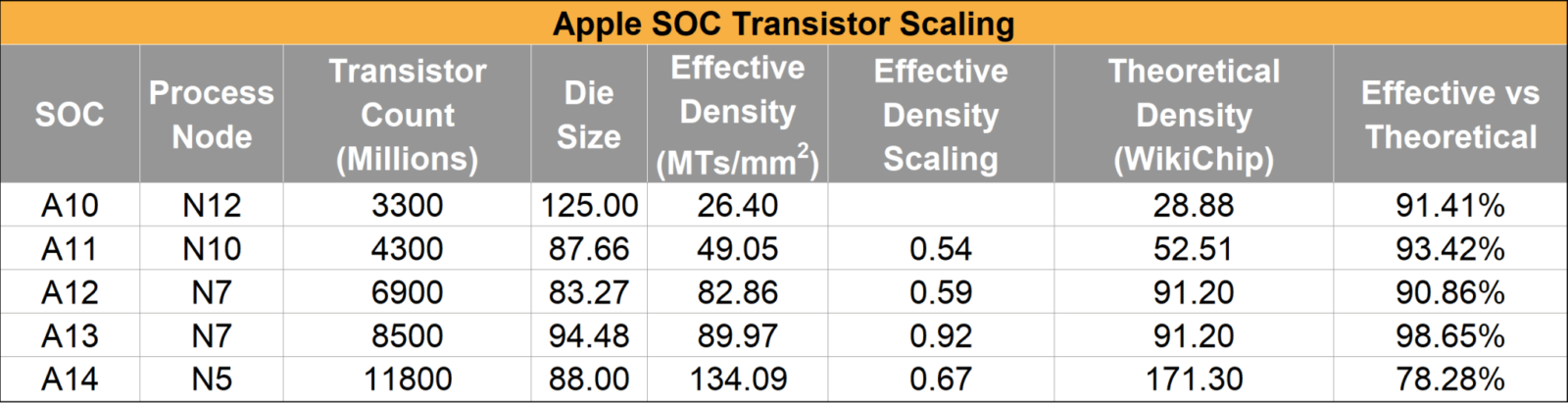

Il SOC A14 Bionic che Apple impiega negli iPhone 12 e negli iPad Air 2020 è il primo nell’intero settore degli smartphone a essere stato costruito con un processo a 5 nanometri. Il processo costruttivo a 5nm permette di offrire prestazioni migliori e ottimizzare i consumi riducendo le dimensioni complessive di componenti. Il nuovo chip è più piccolo rispetto alla generazione precedente, con una dimensione del die di 88 mm² rispetto ai 94,5 mm2 dell’Apple A13. Le dimensioni del die sono inferiori e nonostante questo integra molti più transistor: 11,8 miliardi contro i “soli” 8,5 miliardi dell’A13.

Nonostante queste “prodezze”, il sito specializzato SemiAnalysis evidenzia che sia Apple, sia TSMC sono lontani dalla densità teorica che è possibile ottenere con i 5nm. Con un processo di produzione a 5 nanometri dovrebbe teoricamente essere possibile sfruttare 171,3 milioni di transistor (MT) per mm2, mentre Apple ne sfrutta effettivamente 134, un numero ad ogni modo superiore alle precedenti generazioni create con nodi produttivi a 7nm che consentivano una densità teorica massima di circa 90 MT / mm².

Apple in precedenza si era sempre avvicinata alla densità massima teorica utilizzabile, arrivando lo scorso anno al 98% nel rapporto tra densità effettiva e teorica. L’A14 delude un po’ le aspettative da questo punto di vista con un valore del 78,28%.

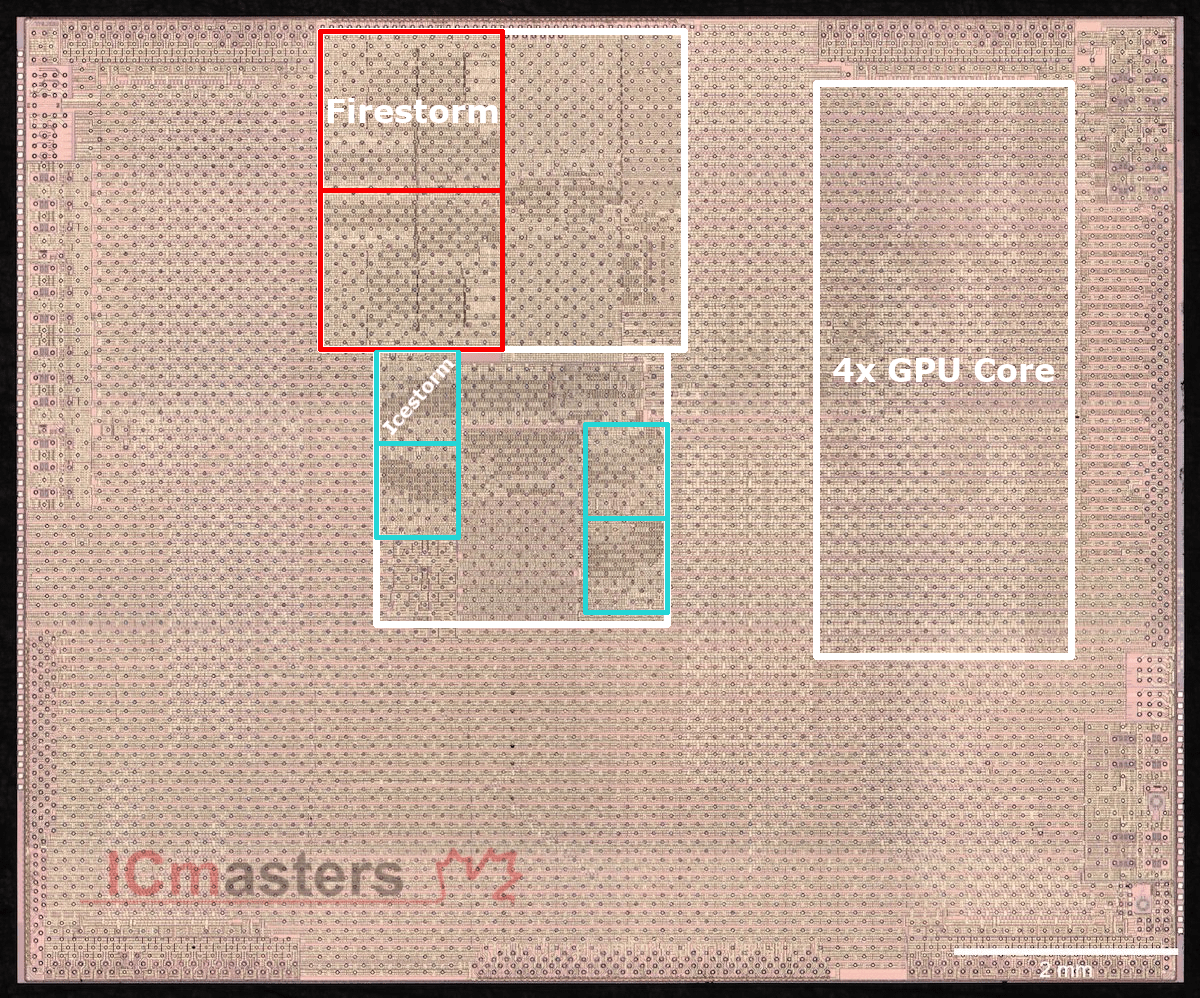

SemiAnalysis rileva che non si tratta ad ogni modo di un fallimento e, a loro dire, la differenza dipende dalla NAND, memoria utilizzata per la cache del processore. Questa componente non è gestista direttamente da Apple o TSMC e quest’anno la sua dimensione non è diminuita. Il SoC A14 di Apple è inciso con un processo produttivo a 5nm ma questo non significa che tutti i suoi componenti siano creati con questo procedimento ed evidentemente la NAND non può essere rimpicciolita quanto gli altri componenti.

Questa differenza tra le dimensioni di memoria NAND e altri transistor non potrà essere colmata presto, secondo SemiAnalysis. Sia TSMC, sia Samsung stanno lavorando su nuove soluzioni, incluso lo stacking della RAM in 3D, una tecnica che a quanto pare è però ancora troppo costosa da sfruttare.