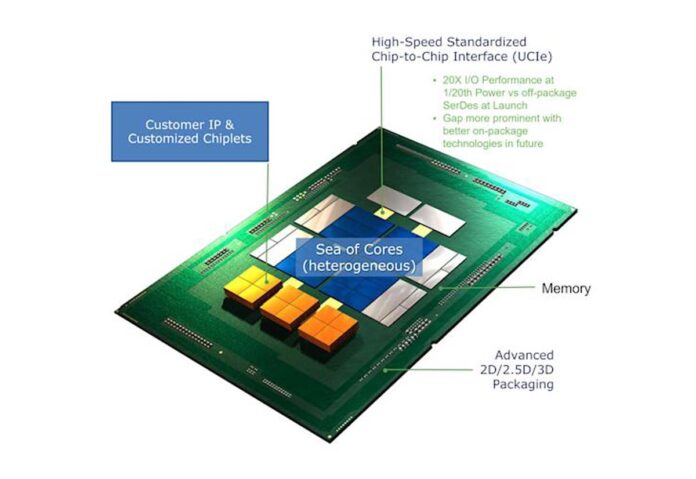

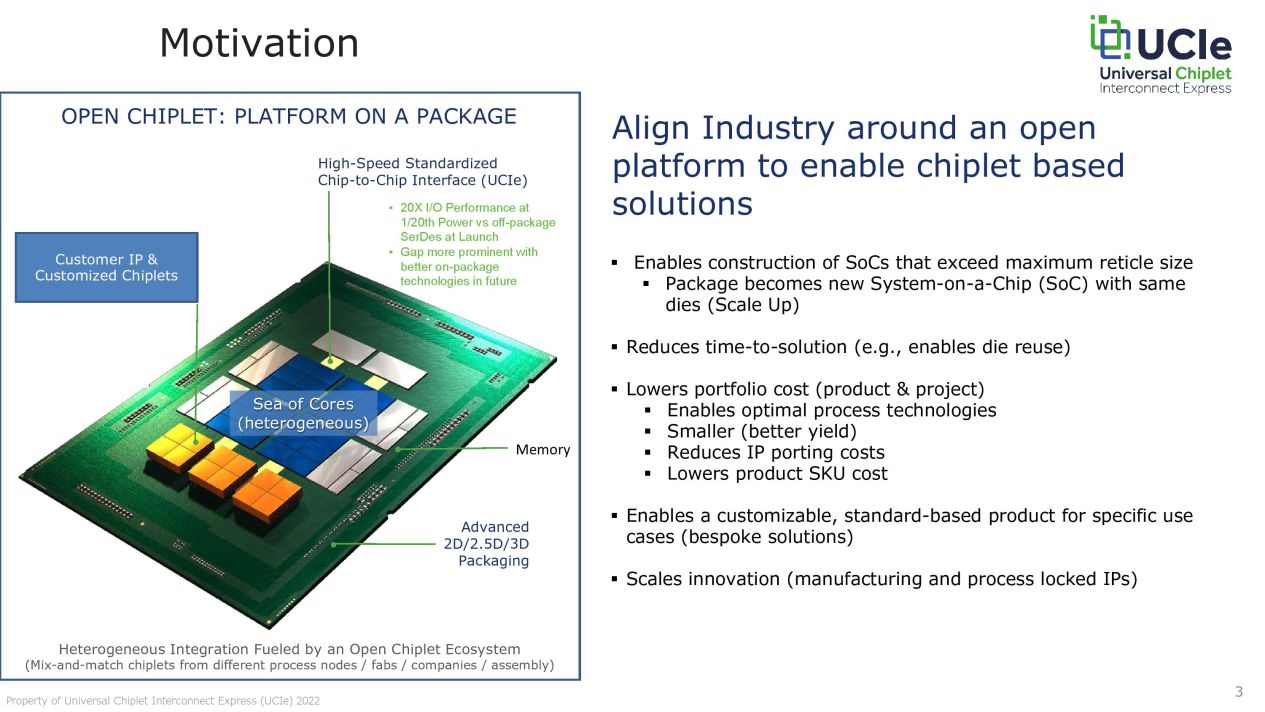

Nell’ambito della produzione dei chip, si sfruttano tecnologie di packaging che permettono di abbinare vari elementi suddividendoli in chiplet più piccoli o tile, dove I/O, SRAM e circuiti di alimentazione vengono fabbricati nel die di base e i chiplet o tile di logica ad elevate prestazioni sono integrati sul livello superiore. I chiplet, in altre parole blocchi di circuiti integrati, sono elementi sempre più comuni nel design dei chip, e alcuni big del mondo IT vorrebbero che questi si diffondessero di più, con vantaggi a supporto della scalabilità progettuale.

Il sito Tom’s Hardware riferisce di una coalizione che include AMD, ARM e Intel, e che ha presentato uno standard denominato Universal Chiplet Interconnect Express (UCIe), pensato per semplificare le connessioni “die-to-die” (il die è la sottile piastrina di materiale semiconduttore sulla quale è stato realizzato il circuito elettronico del circuito integrato), un sistema che potrebbe consentire di mescolare e abbinare chiplet di aziende diverse, creando sistemi on-chip di nuova generazione.

L’alleanza ha già ratificato le specifiche UCIe 1.0 e tra i partner ci sono nomi quali Google, Meta, Microsoft, Qualcomm, Samsung e TSMC.

Sarà probabilmente necessario tempo per vedere chip costruiti tenendo conto di questo nuovo standard, ma il gruppo sta lavorando per definire form factor, protocolli e altri dettagli. Tra i vantaggi di uno standard comune per il collegamento dei componenti elettronici (die), la possibilità di scalare la potenza di elaborazione, abilitando espansioni della CPU più funzionali: si potrebbe velocizzare lo sviluppo di CPU e SoC, usando un design chiplet già pronto, anziché riprogettarlo in proprio. I produttori potrebbero vendere ad altri i chiplet, avere performance più omogenee, consentire a ciascuna azienda di progettare e ottimizzare chiplet per poi combinarli e abbinarli costituendo nuovi sistemi più velocemente, con maggiore potenza elaborativa, utile con nuovi dispositivi ma anche in ambito server per il cloud.