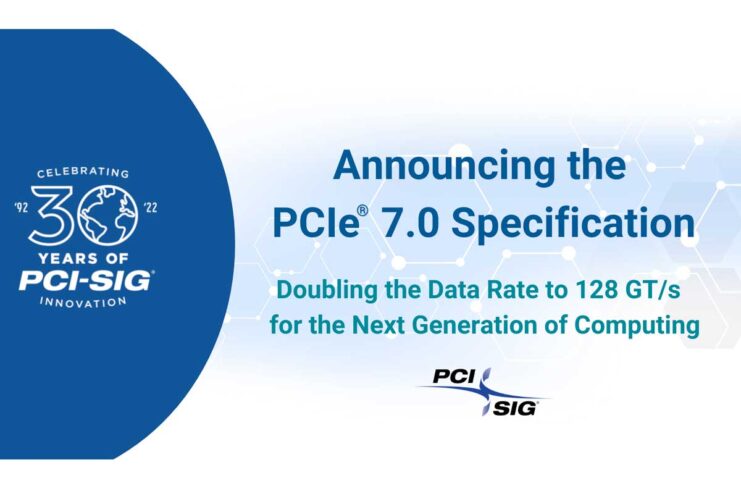

Il PCI-SIG (Peripheral Component Interconnect Special Interest Group) – consorzio di industrie operanti nel campo dell’elettronica che sviluppa gli standard per bus di sistema – ha annunciato PCI Express 7.0, standard che fa un balzo in avanti in termini di prestazioni, nonostante i dispositivi PCI Express 5.0, tardino ancora ad arrivare.

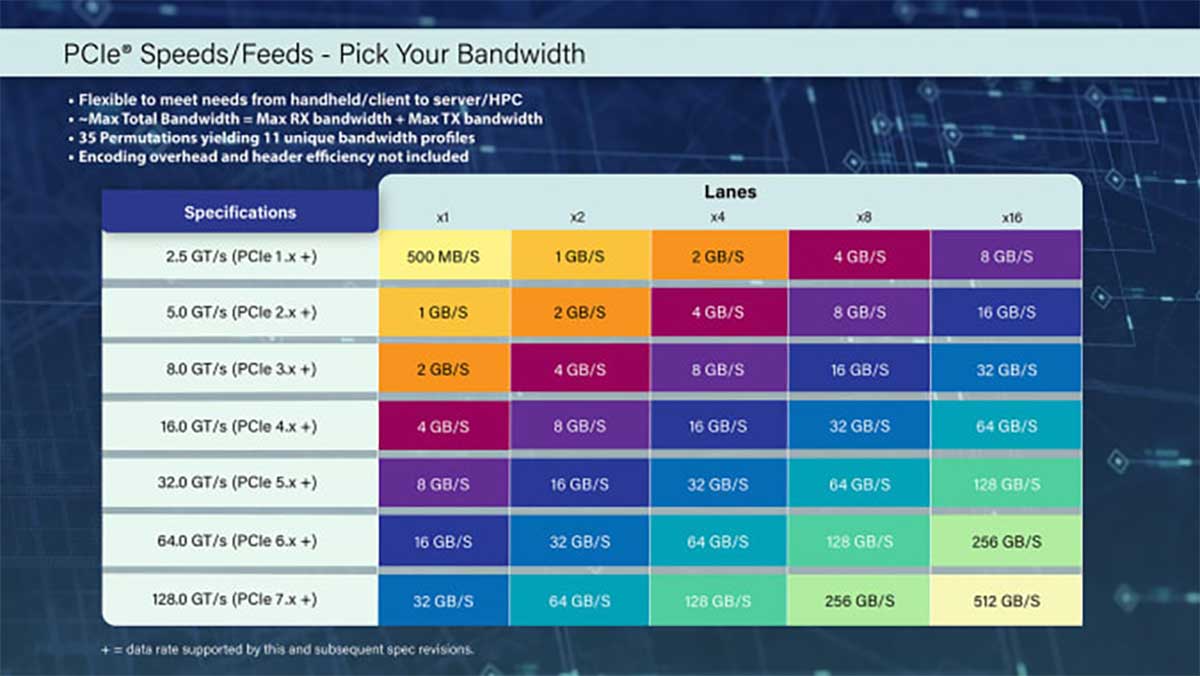

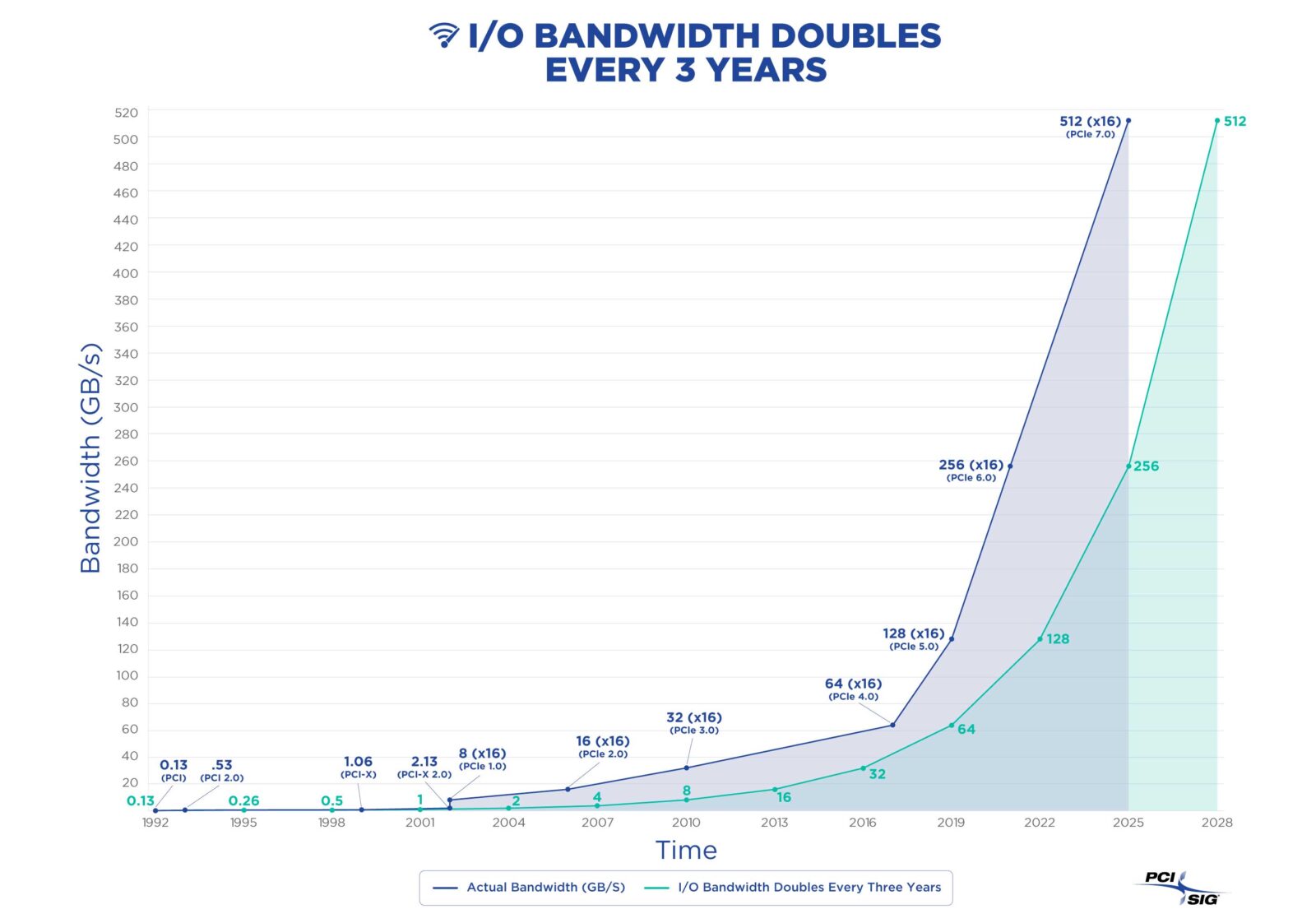

La nuova revisione della specifica promette di incrementare l’ampiezza di banda fino a 512 GB/s, otto volte superiore rispetto allo standard PCI Express 5.0. Sul mercato i primi dispositivi specifici dovrebbero arrivare nel 2025 ma sarà probabilmente necessario aspettare anche oltre prima di vedere effettivamente qualche produttore in grado di sfruttare tale standard.

I 512GB/s teorici sono bidirezionale, sarà disponibile con slot x16, la velocità effettiva sarà probabilmente inferiore ma si tratterà pur sempre di un notevolissimo incremento anche rispetto all’ampiezza di banda dello standard PCI 6.0 previsto per fine anno.

Il PCI-SIG nell’ambito della conferenza annuale dedicata agli sviluppatori ha riferito che l’obiettivo è raddoppiare la velocità di PCI Express ogni tre anni; l’ampiezza di banda dipende ad ogni modo anche da produttori di chip e dispositivi. La 12a generazione di chip Intel Alder Lake presentati a gennaio, supportano PCIe 5.0 ma l’AMD Ryzen 7000 Zen 4 con supporto PCIe 5.0 non arriverà prima dell’autunno. I primi SSD PCIe 5.0 sono arrivati da poco e vantano velocità di lettura fino a 13GB/s.

Altre peculiarità chiave dello standard riguardano migliorie al punto di vista dell’efficienza energetica, una minore latenza e la compatibilità con i precedenti standard.

Le schede madri più moderne offrono PCIe 5.0 e sarà necessario attendere ancora un po’ di tempo prima dell’arrivo di SSD e GPU con supporto per lo standard PCIe 6.0. L’interfaccia PCI Express 7.0 è teoricamente in grado di fornire velocità di trasferimento fino a 128GT/s una connessione bidirezionale di 512GB/s a 16 linee), grazie anche all’accorciamento delle tracce PCIe (diminuirà quindi la anche la distanza minima permessa tra il dispositivo principale PCIe e quello finale) e a schede madri più spesse (da realizzare con materiali di qualità superiore).

![iGuide per i regali di Natale - macitynet..ti CTA Natale iGuida [per Settimio] - macitynet.it](https://www.macitynet.it/wp-content/uploads/2025/12/regali-di-natale-consigli-di-macitynet.jpg)